#### www.maxim-ic.com.cn

#### 特性

- 15 位双向电流测量(DS2740U)

- 1.56µV LSB, ±51.2mV 动态范围

- 78μA LSB, ±2.56A动态范围(20mΩ 外部检流电阻R<sub>SNS</sub>)

- 156μA LSB, ±5.12A动态范围 (10mΩ外部检流电阻R<sub>SNS</sub>)

- 13 位双向电流测量(DS2740BU)

- 6.25µV LSB, ±51.2mV 动态范围

- 312μA LSB, ±2.56A动态范围 (20mΩ外部检流电阻R<sub>SNS</sub>)

- 625μA LSB, ±5.12A动态范围 (10mΩ外部检流电阻R<sub>SNS</sub>)

- 模拟输入滤波器(IS1, IS2)扩展动态范 围用于脉冲负载

- 电流累计寄存器分辨率

- 6.25µVhr (DS2740U 和 DS2740BU)

- 0.3125mAhr (外部 20mΩ R<sub>SNS</sub>)

- 0.6250mAhr (外部 10mΩ R<sub>SNS</sub>)

- Maxim 1-Wire®接口

- 唯一的64位器件地址

- 标准和过驱动时序(OVD)

- 低功耗:

- 工作电流: 最大 65µA

- 休眠电流: 最大 1µA

### 引脚配置

定购信息请参考表1。 详细引脚说明请参考表2。

### 引脚说明

OVD 1-Wire 总线速度选择

PIO 可编程 I/O 引脚

SNS 检流电阻输入

IS2 检流电阻输入

IS1 检流电阻输入

Vss 器件地,电流检流电阻地回路。

DQ 数据输入/输出

V<sub>DD</sub> 电源输入(2.7V至 5.5V)

1-Wire 是 Dallas Semiconductor 的注册商标,Dallas Semiconductor 是 Maxim Integrated Products, Inc.的全資子公司。

1 of 16 051805

### 表 1. 定购信息

| PART         | MARKING          | DESCRIPTION                                            |

|--------------|------------------|--------------------------------------------------------|

| DS2740U      | D2740            | 15-Bit Current Resolution, 8-Pin µMAX                  |

| DS2740U+     | D2740 (see note) | 15-Bit Current Resolution, Lead-Free 8-Pin μMAX        |

| DS2740U/T&R  | D2740            | 15-Bit Current Resolution, 8-Pin µMAX, Tape-and-Reel   |

| DS2740U+T&R  | D2740 (see note) | 15-Bit Current Resolution, Lead-Free 8-Pin μMAX, Tape- |

| D52/400+1&K  | D2740 (See Hote) | and-Reel                                               |

| DS2740BU     | 2740B            | 13-Bit Current Resolution, 8-Pin µMAX                  |

| DS2740BU+    | 2740B (see note) | 13-Bit Current Resolution, Lead-Free 8-Pin µMAX        |

| DS2740BU/T&R | 2740B            | 13-Bit Current Resolution, 8-Pin µMAX, Tape-and-Reel   |

| DS2740BU+T&R | 2740B (see note) | 13-Bit Current Resolution, Lead-Free 8-Pin µMAX, Tape- |

| DSZ/40DU TOK | 2/40D (See Hote) | and-Reel                                               |

注: "+"号标示在封装的第1引脚附近。

### 说明

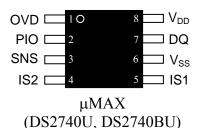

DS2740 非常适合于为成本敏感的应用提供高精度电流流量数据,以实现电池容量监视。电流采用双向测量,动态范围高达 15 位(DS2740U)或 13 位(DS2740BU),净流量在一个 16 位独立寄存器中进行累计。通过 1-Wire 接口,DS2740 允许主系统对其状态和电流测量寄存器进行读/写访问。每个器件都具有工厂编程的 64 位唯一网络地址,允许主系统单独寻址,支持多电池槽协同工作。接口可工作于标准或过驱动时序。

虽然DS2740 主要设计为用于主系统中,但同样也可安装在电池组中。利用DS2740 和FuelPack<sup>TM</sup> 算法,以及主机的温度和电压测量,可构成一个完整而精确的解决方案,用于估计剩余容量。

# 图 1. 方框图

表 2. 详细引脚说明

| PIN         | SYMBOL | DESCRIPTION                                                                                                                                                                                                                    |

|-------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OVD         | 1      | <b>1-Wire Bus Speed Control.</b> Input logic level selects the speed of the 1-Wire bus. Logic 1 selects overdrive (OVD) and Logic 0 selects standard timing (STD). On a multidrop bus, all devices must operate at same speed. |

| PIO         | 2      | <b>Programmable I/O Pin.</b> Programmed as input or output through internal registers. Open-drain output sufficient for LED or vibrator activation.                                                                            |

| SNS         | 3      | Current-Sense Resistor Input                                                                                                                                                                                                   |

| IS2         | 4      | <b>Current-Sense Input.</b> Connected to SNS through a $10k\Omega$ resistor to allow filtering of the current waveform by an external capacitor.                                                                               |

| IS1         | 5      | <b>Current-Sense Input.</b> Connected to $V_{SS}$ through a $10k\Omega$ resistor to allow filtering of the current waveform through an external capacitor.                                                                     |

| $V_{SS}$    | 6      | <b>Device Ground, Current-Sense Resistor Return.</b> Connect directly to the negative terminal of the battery cell.                                                                                                            |

| DQ          | 7      | <b>Data I/O Pin.</b> Operates bidirectionally with open-drain output driver. Internal 1μA pulldown aids in sensing pack removal and Sleep-mode activation.                                                                     |

| $V_{ m DD}$ | 8      | <b>Power-Supply Input.</b> Connects to system voltage supply or positive terminal of battery cell.                                                                                                                             |

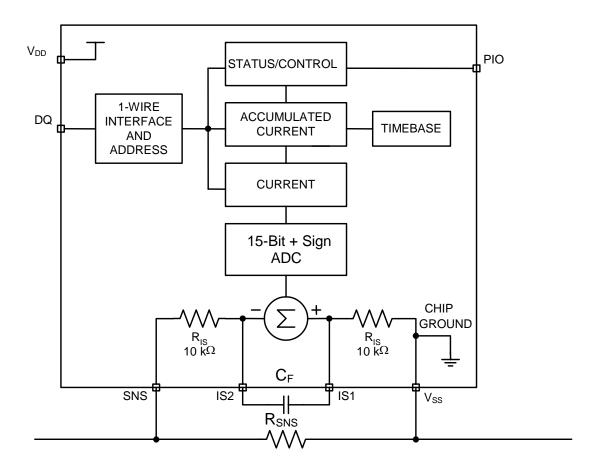

# 图 2. 应用实例

### 供电模式

DS2740 具有两种供电模式:工作模式和休眠模式。在工作模式下,DS2740 作为一个高精度库仑 计连续测量和累计电流,并将结果更新到测量寄存器中。可以对所有寄存器进行读写操作。PIO 引脚处于活动状态。在休眠模式下,DS2740 工作于低功耗模式,不进行电流测量。当V<sub>DD</sub> > 2V 时,可以通过串口对电流、累计电流以及状态/控制寄存器进行访问。

发生下列条件时, DS2740 从休眠模式转换为工作模式:

- 1)  $DQ > V_{IH}$ ,且 $V_{DD} > UV$ 门限,或

- 2) V<sub>DD</sub>从低于UV门限上升至高于UV门限。

发生下列条件时, DS2740 从工作模式转换为休眠模式:

- 1)  $V_{DD}$ 跌落到UV门限以下,或

- 2) SMOD = 1,以及DQ < V<sub>IL</sub>的时间超过 2s。

#### 电流测量

在工作模式下,DS2740 通过测量低阻值检流电阻R<sub>SNS</sub>两端的电压差来持续测量流入和流出电池的电流。为了扩展脉冲型负载电流的输入范围,可以在IS1 和IS2 引脚之间连接一个电容以对该电压信号进行滤波。外部电容和两个内部电阻在ADC输入端形成了一个低通滤波器。IS1 和IS2 之间的电压检测范围为±51.2mV。转换周期内,只要连续信号或平均信号电平(滤波后)不超过±51.2mV,则可对幅度可高达 102mV的输入峰值信号进行转换。ADC以 18.6kHz的速率对IS1 和IS2 之间的输入进行差分采样,并在每个转换周期完成时更新电流寄存器。各种分辨率选项时的转换时间在下面的表格中列出。可提供两种分辨率选项。图 3 给出了各种选项中电流测量寄存器的格式和分辨率。"S"表示符号位。

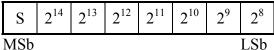

### 图 3. 电流寄存器格式

**DS2740U**: Units:  $1.5625\mu V/R_{SNS}$ , 15-bit + sign resolution, 3.5s conversion period. **DS2740BU**: Units:  $6.250\mu V/R_{SNS}$ , 13-bit + sign resolution, 0.875s conversion period.

MSB—Address 0Eh

LSB—Address 0Fh

LSb MSb LSb

$2^{5}$

$2^6$

Full-scale magnitude: ±51.2mV

|          | GONNEDGION      | CURRENT RESOLUTION (1 LSB)          |              |                       |                       |         |  |  |

|----------|-----------------|-------------------------------------|--------------|-----------------------|-----------------------|---------|--|--|

| PART     | CONVERSION TIME | V <sub>IS1</sub> - V <sub>IS2</sub> | $ m R_{SNS}$ |                       |                       |         |  |  |

|          |                 |                                     | 20mΩ         | $15 \mathrm{m}\Omega$ | $10 \mathrm{m}\Omega$ | 5mΩ     |  |  |

| DS2740U  | 3.515s          | 1.5625µV                            | 78.13μA      | 104.2μΑ               | 156.3μΑ               | 312.5µA |  |  |

| DS2740BU | 0.878s          | 6.250µV                             | 312.5μΑ      | 416.7μΑ               | 625μΑ                 | 1.250mA |  |  |

每进行第 1024 次转换时,ADC 测量其输入失调以进行失调校准。在 DS2740U 中,大约每小时进行一次失调校准,而在 DS2740BU 中,则大约每小时进行四次。所得到的校准系数用来校准随后的 1023 次测量结果。在输入失调转换过程中,ADC 不测量 IS1 和 IS2 两端的信号。累计电流寄存器(ACR)中的最大误差可能达到 1/1024;但为了减小该误差,电流寄存器采用失调转换前的那次电流测量结果替代电流累计过程中漏掉的电流测量。这就使得失调校准所带来的累计电流误差远小于 1/1024。

### 电流累计

每一次转换周期结束时,电流测量值在片内求和或累计,累计结果存储在累计电流寄存器(ACR)内。ACR 的精度取决于电流测量精度和转换时基精度。ACR 的范围为±204.8mVh,一个 LSb 为6.25μVh。额外的存储器保留了每次累计结果的小数部分,但用户无法访问这些位。

可以对 ACR 进行读和写访问。写操作 ACR 将清除小数累计结果。同时,写 ACR 时,将强制 ADC 测量其失调并更新内部失调校准因数。在写 ACR 后的第二次转换时开始电流测量和累计。图 4 给出了 ACR 的地址、格式和分辨率。

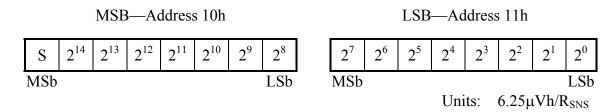

### 图 4. 电流累计寄存器的格式

|          |                    |                               |                       | ACR LSB               |                       |                      |  |  |

|----------|--------------------|-------------------------------|-----------------------|-----------------------|-----------------------|----------------------|--|--|

| PART     | UPDATE<br>INTERVAL | $V_{\rm IS1}$ - $V_{\rm IS2}$ | $ m R_{SNS}$          |                       |                       |                      |  |  |

|          |                    |                               | $20 \mathrm{m}\Omega$ | $15 \mathrm{m}\Omega$ | $10 \mathrm{m}\Omega$ | $5 \mathrm{m}\Omega$ |  |  |

| DS2740U  | 3.515s             | 6.25µVh                       | 212 5 A b             | 416 7u Ab             | 625µAh                | 1.250mAh             |  |  |

| DS2740BU | 0.878s             | 0.23μ ν 11                    | 312.5µAh              | 416.7μAh              | 023μAn                | 1.230IIIAII          |  |  |

|          |                                     | A                     | CR RANGE              |                       |                      |  |  |

|----------|-------------------------------------|-----------------------|-----------------------|-----------------------|----------------------|--|--|

| PART     | V <sub>IS1</sub> - V <sub>IS2</sub> | $R_{ m SNS}$          |                       |                       |                      |  |  |

|          | <b>v</b> IS1 - <b>v</b> IS2         | $20 \mathrm{m}\Omega$ | $15 \mathrm{m}\Omega$ | $10 \mathrm{m}\Omega$ | $5 \mathrm{m}\Omega$ |  |  |

| DS2740U  | ±204.8mVh                           | ±10.24Ah              | ±13.65Ah              | ±20.48Ah              | ±40.96Ah             |  |  |

| DS2740BU | ±∠04.8III V II                      | ±10.24AII             | ±13.03AII             | ±∠0.48AII             | ±40.90AII            |  |  |

### 存储器

DS2740 具有作为测量、状态指示和控制寄存器的存储器空间。读取双字节寄存器的 MSB 时,MSB 和 LSB 同时被锁存,并且在读数据命令期间保持不变,以防止在读取数据期间刷新 LSB,保证两个寄存器字节之间的同步。为获得一致的结果,务必在同一个读数据命令期间读取双字节寄存器的 MSB 和 LSB。

### 表 3. 存储器映射

| ADDRESS (HEX) | DESCRIPTION                      | READ/WRITE |

|---------------|----------------------------------|------------|

| 00            | Reserved                         | _          |

| 01            | Status Register                  | R/W        |

| 02 to 07      | Reserved                         | _          |

| 08            | Special Feature Register         | R/W        |

| 09 to 0D      | Reserved                         | _          |

| 0E            | Current Register MSB             | R          |

| 0F            | Current Register LSB             | R          |

| 10            | Accumulated Current Register MSB | R/W        |

| 11            | Accumulated Current Register LSB | R/W        |

| 12 to FF      | Reserved                         | _          |

### 状态寄存器

状态寄存器的格式如图 5 所示。各位的功能将在下面的段落中详细说明。

## 图 5. 状态寄存器格式

#### ADDRESS 01h

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Χ     | SMOD  | X     | RNAOP | Χ     | Х     | Х     | Χ     |

**SMOD**—休眠模式使能。该位的值为 1 时,允许 DS2740 在 DQ 被拉低的时间超过 2s 后进入休眠模式;为 0 时禁止与 DQ 相关的休眠模式转换。上电缺省状态为 SMOD = 0。

**RNAOP**—读网络地址操作码。该位为 0 时设置读网络地址命令的操作码为 33h,为 1 时设置操作码为 39h。上电复位状态为 RNAOP = 0。

X—保留位。

### 特殊功能寄存器

特殊功能寄存器的格式如图 6 所示。各位的功能将在下面的段落中详细说明。

### 图 6. 特殊功能寄存器格式

#### ADDRESS 08h

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Χ     | PIO   | Х     | Х     | Х     | X     | Х     | Х     |

PIO—PIO引脚检测和控制。该位可进行读和写。PIO位写 0 时将使能PIO漏极开路输出驱动器, 拉低PIO引脚。PIO位写 1 时将禁止输出驱动器,允许PIO引脚拉高或用作输入。读PIO位将返回 PIO引脚的逻辑电平。注:如果PIO悬空,弱下拉将拉低该引脚。在初始上电、DS2740 进入休眠 模式或DQ为低的时间超过t<sub>SLEEP</sub> (与SMOD引脚的状态无关)时,PIO复位至 1。

X—保留位。

### 1-Wire 总线系统

1-Wire 总线是具有单个主机和一个或多个从机的系统。多节点总线是挂接了多个从机的 1-Wire 总线。而单节点总线上仅具有一个从机设备。在任何情况下,DS2740 都是从机。主机系统中的总线主机通常是一个微处理器。对该总线系统的讨论分为四个部分: 64 位网络地址、硬件配置、处理流程以及 1-Wire 信令。

### 64位网络地址

每个 DS2740 都带有唯一的、由工厂设置的 64 位 1-Wire 网络地址。前 8 位是 1-Wire 家族码 (DS2740 的家族码为 36h)。之后的 48 位是唯一序列码。最后 8 位是前 56 位的循环冗余校验码 (CRC) (参见图 7)。64 位网络地址和器件内置的 1-Wire I/O 电路允许 DS2740 通过 1-Wire 协议与主机通信,1-Wire 协议的详细说明见本数据资料的 1-Wire 总线系统一节。

## 图 7.1-Wire 网络地址格式

| 8-BIT CRC | 48-BIT SERIAL NUMBER | 8-BIT FAMILY<br>CODE (36h) |

|-----------|----------------------|----------------------------|

| MSb       |                      | LSb                        |

### CRC 校验

DS2740 带有 8 位 CRC 校验码,存储在 1-Wire 网络地址的最高字节中。为了确保地址的无差错传输,主机系统可根据网络地址的前 56 位计算出 CRC 校验码,并与来自 DS2740 的 CRC 进行比较。系统主机验算该 CRC 值并根据结果采取相应措施。DS2740 不比较 CRC 校验码,也不会在CRC 不匹配时阻止命令的继续执行。正确使用 CRC 可使通信信道具有极高的完整性。

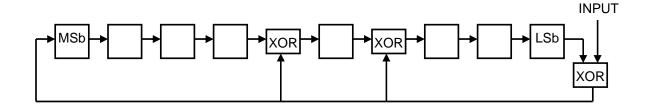

主机可利用图 8 所示的由移位寄存器和异或门组成的电路生成CRC,也可由软件生成CRC。更多有关Maxim 1-Wire CRC的信息请参考应用笔记 27: *理解和运用Maxim iButton®产品中的循环冗余 校验(CRC)*。(该应用笔记可从Maxim的公司网站www.maxim-ic.com.cn下载。)

在图 8 所示的电路中,首先将移位寄存器的各位初始化为 0。然后从家族码的最低有效位开始逐位移入。移入家族码的第 8 位后,开始移入序列号。序列号的第 48 位移入后,移位寄存器中的值就是 CRC 值。

### 图 8.1-Wire CRC 校验框图

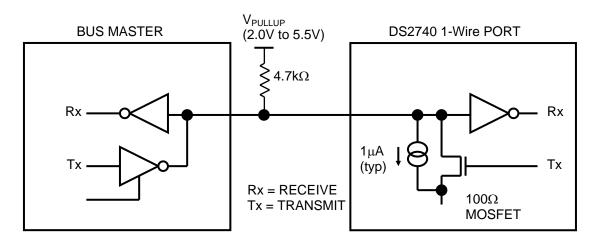

#### 硬件配置

由于 1-Wire 总线系统中仅具有一根数据线,因此在适当的时间驱动总线上的各个设备非常重要。 为简化操作,挂接在 1-Wire 总线上的各器件都必须通过漏极开路或三态输出驱动器来连接总线。 DS2740 采用漏极开路输出驱动器作为双向接口电路,如图 9 所示。如果总线主机没有可利用的双向引脚,可将独立的输入和输出引脚连接在一起。

1-Wire 总线要求在总线主机侧连接一个上拉电阻。对于较短的数据线长度,该电阻的值约为5kΩ。1-Wire 总线的空闲状态为高电平。如果由于某种原因需要暂停总线操作,总线必须保持在空闲状态以便稍后恢复操作。如果总线保持低电平的时间超过 120μs (在高速模式下为 16μs),则总线上的从器件会将该低电平周期理解为复位脉冲,从而终止操作。

DS2740 可运行于两种通信速率模式,即标准速率模式和高速模式。速率模式由 OVD 引脚的输入逻辑电平确定,逻辑 0 选择标准速率模式,而逻辑 1 选择高速模式。在以复位脉冲发起操作之前,OVD 引脚必须保持为稳定的逻辑 0 或 1。多节点总线上所有 1-Wire 器件必须运行于相同的通信速率,以实现正常工作。标准速率模式和高速模式的 1-Wire 时序在 *Electrical Characteristics: 1-Wire Interface* 表格中列出。

### 图 9.1-Wire 总线接口电路

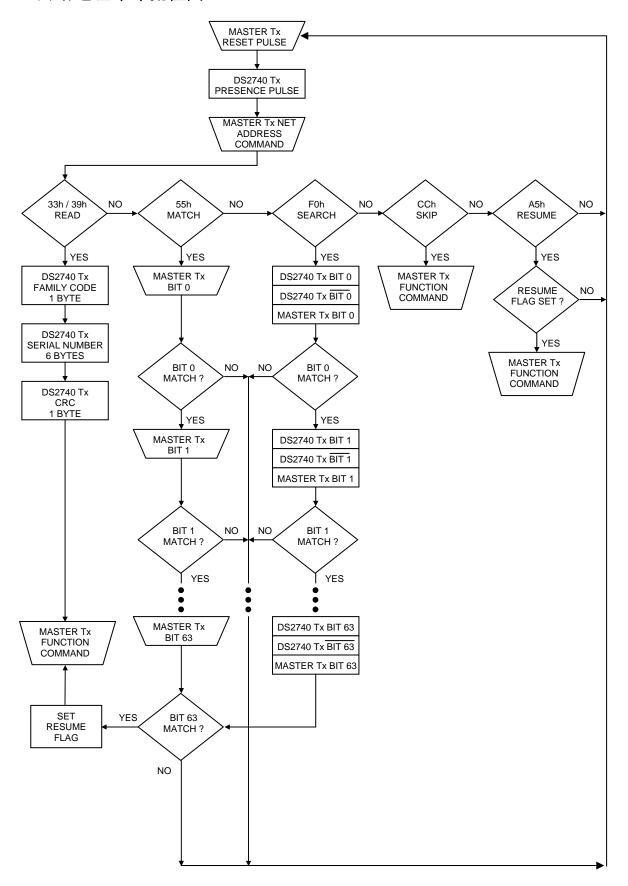

#### 处理流程

通过 1-Wire 端口访问 DS2740 的协议如下:

- 初始化

- 网络地址命令

- 功能命令

- 传输/数据

以下各章节将详细说明这些步骤。

1-Wire 总线的所有操作都以初始化过程开始,由总线主机发送的复位脉冲以及 DS2740 和总线上其他从机同时发出的在线应答脉冲组成。在线应答脉冲向总线主机报告总线上的一个或多个从设备已准备就绪。更多详细信息请参考 1-Wire 信令章节。

### 网络地址命令

总线主机检测到一个或多个从设备的应答脉冲后,可发送下列各段落所描述的网络地址命令之一。在方括号中,各网络地址命令的名称后是该命令的8位操作码。图10给出了网络地址命令的流程图。

**Read Net Address [33h 或 39h]**: 该命令允许总线主机读取 DS2740 的 1-Wire 网络地址。只有当总线上挂接单个从机设备时才能使用该命令。如果总线上挂接了多个从机设备,则所有从机试图同时发送数据时(漏极开路产生"线与"结果),将会发生数据冲突。状态寄存器的 RNAOP 位选择该命令的操作码,RNAOP = 0表示操作码为 33h, RNAOP = 1表示操作码为 39h。

**Match Net Address [55h]:** 该命令允许总线主机访问 1-Wire 总线上某个特定的 DS2740。只有被寻址的 DS2740 才会响应随后的功能命令。所有其他从机设备忽略功能命令并等待复位脉冲。该命令适用于总线上挂接一个或多个从机的情况。

Skip Net Address [CCh]: 总线上仅有一个 DS2740 时,该命令允许总线主机在不指定从设备地址的情况下发送功能命令,从而节约时间。如果总线上挂接了多个从机,所有从机在随后的功能命令中同时发送数据会产生数据冲突。

Search Net Address [F0h]: 该命令允许总线主机采用排除法来识别总线上所有从机的 1-Wire网络地址。该搜索过程重复三个简单的步骤: 读一位、读该位的补码、然后写入该位的期望值。总线主机对网络地址的每一位都执行这个简单的三步流程。在完整的遍历所有 64 位之后,总线主机可得到一个从机地址。然后,可通过反复执行该过程识别其余从机的地址。有关网络地址搜索的全面讨论,请参阅Book of DS19xx iButton Standards的第 5 章,其中还包括一个实例。(该资料可从Maxim公司的网站www.maxim-ic.com.cn下载。)

**Resume** [A5h]: 在多节点应用环境中需要多次访问 DS2740 时,该命令可提高数据吞吐能力。 Resume 与 Skip Net Address 命令类似,不必在每次访问 DS2740 时都发送 64 位网络地址。在成功执行 Match Net Address 命令或 Search Net Address 命令后,DS2740 内的一个标志会置位。当该标志置 1 后,便可通过 Resume 命令重复访问 DS2740。访问总线上的其他从机时会清除该标志,从而避免了两个或多个从机同时响应 Resume 命令。

#### 功能命令

在成功执行一个网络地址命令之后,总线主机可通过下列各段落所描述的任意功能命令来访问 DS2740,这些命令的总结在表 4 中列出。在方括号中列出了各功能命令的名称,后面为该命令的 8 位操作码。

Read Data [69h, XX]: 该命令从存储器地址 XX 开始读取 DS2740 的数据。地址的最高位输入后,可立刻读取地址 XX 中数据的最低位。因为接收到每个数据字节的最高位之后,地址自动递增,因此收到地址 XX 中数据的最高位之后,可立刻即读取地址 XX + 1 中数据的最低位。如果总线主机持续读取超出 FFh 的地址,DS2740 将重新从地址 00 开始输出数据。存储器映射表中标为"Reserved"的地址包含不确定的数据。在位流的任何位置,均可由总线主机发出复位脉冲来终止 Read Data 命令。

Write Data [6Ch, XX]: 该命令从存储器地址 XX 开始将数据写入 DS2740。输入地址的最高位之后,可立即写入要存储在地址 XX 处的数据最低位。因为写入每个数据字节的最高位之后地址自动递增,因此写入要存储到地址 XX 处的数据最高位之后,可立即写入要存储在地址 XX + 1 处的数据最低位。如果总线主机持续写操作超出 FFh 的地址,DS2740 将重新从地址 00 开始写入。对只读地址、保留地址的写操作将被忽略。不完整的字节将不被写入。更多详细信息请参考存储器章节。

## 图 10. 网络地址命令流程图

### 表 4. 功能命令

| COMMAND    | DESCRIPTION                                   | COMMAND PROTOCOL | BUS STATE<br>AFTER COMMAND<br>PROTOCOL | BUS DATA                |

|------------|-----------------------------------------------|------------------|----------------------------------------|-------------------------|

| Read Data  | Reads data from memory starting at address XX | 69h, XX          | Master Rx                              | Up to 256 bytes of data |

| Write Data | Writes data to memory starting at address XX  | 6Ch, XX          | Master Tx                              | Up to 256 bytes of data |

### 1-Wire 信令

1-Wire 总线需要严格的信令协议来保证数据的完整性。DS2740 使用以下四种信令协议: 初始化过程(复位脉冲和随后的在线应答脉冲)、写 0、写 1 以及读数据。除了在线应答脉冲以外,所有其他信令均由总线主机发出。

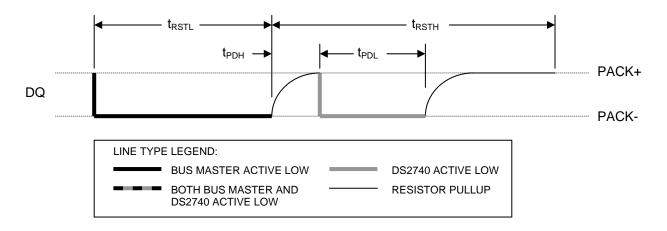

开始与DS2740 进行任何通信都必需的初始化过程在图 11 中给出。复位脉冲之后的在线应答脉冲表明DS2740 已经准备好接收网络地址命令。总线主机发出(Tx) t<sub>RSTL</sub>宽的复位脉冲,然后总线主机释放数据线,进入接收模式(Rx)。之后上拉电阻将 1-Wire总线拉至高电平。DS2740 检测到DQ引脚的上升沿后等待t<sub>PDH</sub>时间,然后发出t<sub>PDL</sub>宽的在线应答脉冲。

### 图 11.1-Wire 初始化时序

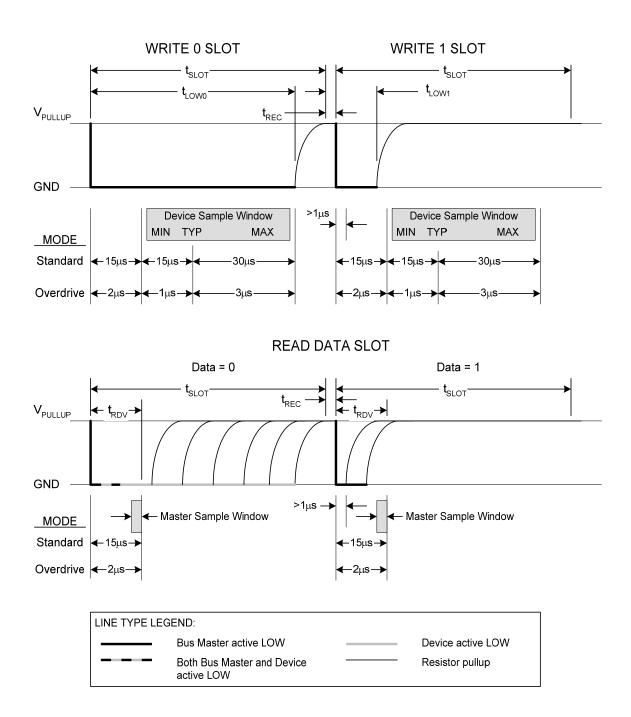

### 写时隙

写时隙以总线主机将 1-Wire总线从逻辑高(无效)电平拉至逻辑低电平开始。写时隙有两种类型:写 1 和写 0。所有写时隙必须保持t<sub>SLOT</sub>时间,并且写时隙之间需要 1μs的最小恢复时间(t<sub>REC</sub>)。DS2740将在线路下降沿之后的 15μs至 60μs之间(高速模式下在 2μs至 6μs之间)采样 1-Wire总线数据。如果采样时总线为高电平,则为写 1 时隙。如果采样时总线为低电平,则为写 0 时隙(参见图 12)。总线主机若要产生写 1 时隙,必须先拉低总线,然后释放以允许其在写时隙开始后的 15μs (高速模式下为 2μs)内拉为高电平。主机若要产生写 0 时隙,必须拉低总线,并在写时隙持续时间内保持为低电平。

### 读时隙

读时隙以总线主机将 1-Wire总线从逻辑高电平拉至逻辑低电平开始。总线主机必须使总线保持低电平的时间至少持续 1μs,然后再释放总线允许DS2740 输出有效数据。总线主机在读时隙开始t<sub>RDV</sub>时间后采样数据。DS2740 在读时隙结束时释放总线,允许外部上拉电阻将其拉至高电平。所有读时隙必须持续t<sub>SLOT</sub>,并且在读时隙之间需要 1μs的最小恢复时间(t<sub>REC</sub>)。详细信息参见图 12。

### 图 12.1-Wire 写时隙和读时隙

### **ABSOLUTE MAXIMUM RATINGS\***

$\begin{array}{lll} \mbox{Voltage on $V_{DD}$, DQ, IS1, IS2, PIO, Relative to $V_{SS}$} & -0.3V \ \mbox{to } +6V \\ \mbox{Voltage on SNS, Relative to $V_{SS}$} & -0.3V \ \mbox{to } +6V \\ \mbox{Operating Temperature Range} & -40^{\circ}\mbox{C to } +85^{\circ}\mbox{C} \\ \mbox{Storage Temperature Range} & -55^{\circ}\mbox{C to } +125^{\circ}\mbox{C} \\ \end{array}$

Soldering Temperature See IPC/JEDECJ-STD-020A

### RECOMMENDED DC OPERATING CONDITIONS

$(2.7V \le V_{DD} \le 5.5V; T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER      | SYMBOL      | CONDITIONS | MIN  | TYP | MAX  | UNITS |

|----------------|-------------|------------|------|-----|------|-------|

| Supply Voltage | $V_{ m DD}$ | (Note 1)   | 2.7  |     | 5.5  | V     |

| Data Pin       | DQ          | (Note 1)   | -0.3 |     | +5.5 | V     |

#### DC ELECTRICAL CHARACTERISTICS

$(2.7V \le V_{DD} \le 4.2V; T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                         | SYMBOL              | CONDITIONS                                            | MIN                    | TYP    | MAX            | UNITS            |

|-----------------------------------|---------------------|-------------------------------------------------------|------------------------|--------|----------------|------------------|

| Active Current                    | ī                   |                                                       |                        | 50     | 65             | 4                |

| Active Current                    | I <sub>ACTIVE</sub> | $V_{DD} = 5.5V$                                       |                        |        | 85             | μΑ               |

|                                   |                     | $V_{DD} = 2.0V$ ,                                     |                        | 0.6    | 1.0            |                  |

| Sleep-Mode Current                | I <sub>SLEEP</sub>  | $DQ = PIO = V_{SS}$                                   |                        | 0.0    | 1.0            | μΑ               |

| Sitop wiede current               | -SLEET              | $V_{DD} = 4.2V$ ,                                     |                        | 0.9    | 1.25           | pv2 1            |

| T. 1 1, C1                        |                     | $DQ = PIO = V_{SS}$                                   |                        |        |                |                  |

| Undervoltage Sleep<br>Threshold   | $V_{\mathrm{UV}}$   |                                                       | 2.3                    | 2.5    | 2.7            | V                |

| Current Resolution                | $I_{LSB}$           | DS2740U                                               |                        | 1.5625 |                | $\mu V/R_{SNS}$  |

|                                   | ILSB                | DS2740BU                                              |                        | 6.25   |                | μV/KSNS          |

| Current Full-Scale Magnitude      | $I_{FS}$            |                                                       |                        | 51.2   |                | $mV/R_{\rm SNS}$ |

| Current Measurement               |                     | DS2740U (Note 2)                                      | -3                     | +1     | +5             |                  |

| Offset (Auto<br>Calibrated)       | $I_{OERR}$          | DS2740BU (Note 2)                                     | -2                     | 0      | +2             | LSb              |

| Current Gain Error                | $I_{GERR}$          |                                                       | -1                     |        | +1             | % of reading     |

| Accumulated Current Resolution    | q <sub>CA</sub>     |                                                       |                        | 6.25   |                | μVh              |

| Current Sample Clock<br>Frequency | $ m f_{SAMP}$       |                                                       |                        | 18.6   |                | kHz              |

| Timebase Accuracy                 | +                   | $V_{\rm DD} = 3.5 \text{V at } +25 ^{\circ} \text{C}$ | -1                     |        | +1             | %                |

| Timebase Accuracy                 | $t_{\rm ERR}$       |                                                       | -4                     |        | +4             | 70               |

| Input Logic High:<br>OVD          | $V_{ m IH}$         | (Note 1)                                              | V <sub>DD</sub> - 0.2V |        |                | V                |

| Input Logic High: DQ,<br>PIO      | $V_{\mathrm{IH}}$   | (Note 1)                                              | 1.5                    |        |                | V                |

| Input Logic Low:<br>OVD           | $V_{IL}$            | (Note 1)                                              |                        |        | $V_{SS} + 0.2$ | V                |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

| Input Logic Low: DQ,<br>PIO       | $V_{\mathrm{IL}}$ | (Note 1)                            |     |     | 0.6 | V  |

|-----------------------------------|-------------------|-------------------------------------|-----|-----|-----|----|

| Output Logic Low:<br>DQ, PIO      | $V_{OL}$          | $I_{OL} = 4mA \text{ (Note 1)}$     |     |     | 0.4 | V  |

| DQ, PIO Input<br>Pulldown Current | $I_{PD}$          | $V_{DD} = 4.2V,$<br>$V_{DQ} = 0.4V$ |     | 0.5 |     | μА |

| OVD Input Leakage                 | IL <sub>OVD</sub> | PIO bit = 1                         | -1  |     | 1   | μA |

| DQ Capacitance                    | $C_{DQ}$          |                                     |     |     | 50  | pF |

| DQ Low to Sleep Time              | $t_{ m SLEEP}$    | (Note 3)                            | 2.0 |     | 2.4 | S  |

# **ELECTRICAL CHARACTERISTICS: 1-Wire INTERFACE—STANDARD SPEED**

$(2.7V \le V_{DD} \le 5.5V; T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER            | SYMBOL        | MIN | TYP | MAX | UNITS |

|----------------------|---------------|-----|-----|-----|-------|

| Time Slot            | $t_{ m SLOT}$ | 60  |     | 120 | μs    |

| Recovery Time        | $t_{ m REC}$  | 1   |     |     | μS    |

| Write 0 Low Time     | $t_{ m LOW0}$ | 60  |     | 120 | μS    |

| Write 1 Low Time     | $t_{ m LOW1}$ | 1   |     | 15  | μS    |

| Read Data Valid      | $t_{ m RDV}$  |     |     | 15  | μS    |

| Reset Time High      | $t_{ m RSTH}$ | 480 |     |     | μS    |

| Reset Time Low       | $t_{ m RSTL}$ | 480 |     | 960 | μS    |

| Presence Detect High | $t_{ m PDH}$  | 15  | •   | 60  | μS    |

| Presence Detect Low  | $t_{ m PDL}$  | 60  | •   | 240 | μS    |

## **ELECTRICAL CHARACTERISTICS: 1-Wire INTERFACE—OVERDRIVE SPEED**

$(2.7V \le V_{DD} \le 5.5V; T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER            | SYMBOL             | MIN | TYP | MAX | UNITS |

|----------------------|--------------------|-----|-----|-----|-------|

| Time Slot            | $t_{ m SLOT}$      | 6   |     | 16  | μs    |

| Recovery Time        | $t_{ m REC}$       | 1   |     |     | μs    |

| Write 0 Low Time     | $t_{ m LOW0}$      | 6   |     | 16  | μs    |

| Write 1 Low Time     | $t_{\rm LOW1}$     | 1   |     | 2   | μs    |

| Read Data Valid      | $t_{ m RDV}$       |     |     | 2   | μs    |

| Reset Time High      | $t_{RSTH}$         | 48  |     |     | μs    |

| Reset Time Low       | $t_{ m RSTL}$      | 48  |     | 80  | μs    |

| Presence Detect High | $t_{\mathrm{PDH}}$ | 2   |     | 6   | μs    |

| Presence Detect Low  | $t_{\mathrm{PDL}}$ | 8   | ·   | 24  | μs    |

**Note 1:** All voltages are referenced to  $V_{SS}$ .

**Note 2:** Offset performance requires proper circuit layout design free of surface contaminants.

**Note 3:** The DS2740 enters the Sleep mode 2.0s to 2.4s after DQ goes low.